基于DE1-SOC开发板的oneAPI实验教程(2)

- 期货快讯

- 2025-07-16

- 34060

本期我们介绍在DE1-SoC开发板的FPGA上实现并部署Simple DMA和Simple Adder两个案例。

上一期我们从oneAPI CLI Samples Browser复制保存的Simple DMA是基于Quartus Pro的Nios V示例,无法直接用在DE1-SoC开发板上,因此这一节我们用的Simple DMA是基于Quartus Standard的Nios II 示例,后续会计划用新版Quartus Standard软件将DE1-SoC的oneAPI示例升级到Nios V。

注:请复制链接http://mail.terasic.com.cn/~bingxia/My_First_oneAPI_de1_soc.zip到浏览器去下载My_First_oneAPI_de1_soc BSP,内含example code。

一、配置Simple DMA IP

使用oneAPI DPC++/C++编译器可以将Simple DMA编译成RTL IP硬件模块,然后将RTL IP集成到FPGA,使用Plarform Designer可以将该IP核集成到设计中。

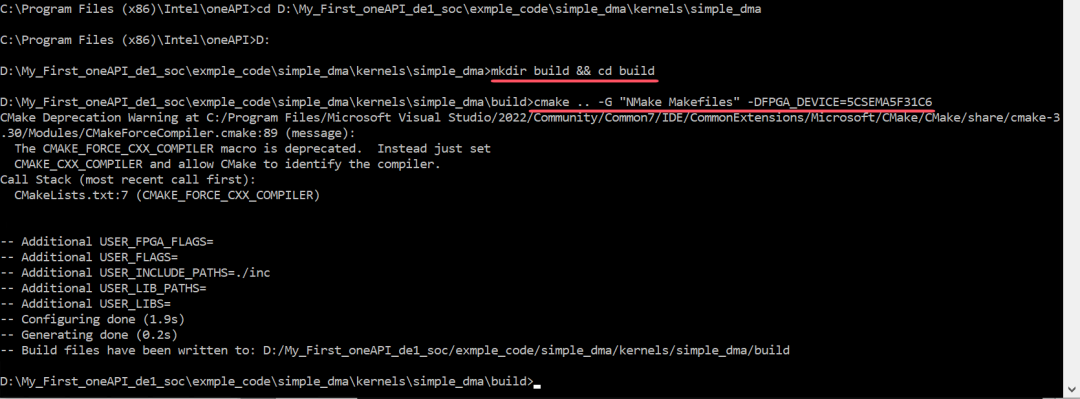

1. 打开Intel oneAPI命令窗口,切换到My_First_oneAPI_de1_socexmple_codesimple_dmakernelssimple_dma路径,执行以下命令创建build文件夹,并指定FPGA为DE1-SoC开发板的5CSEMA5F31C6。

mkdir build && cd build

cmake .. -G "NMake Makefiles" -DFPGA_DEVICE=5CSEMA5F31C6

2. 执行nmake report编译DMA IP,生成IP组件及优化报告。

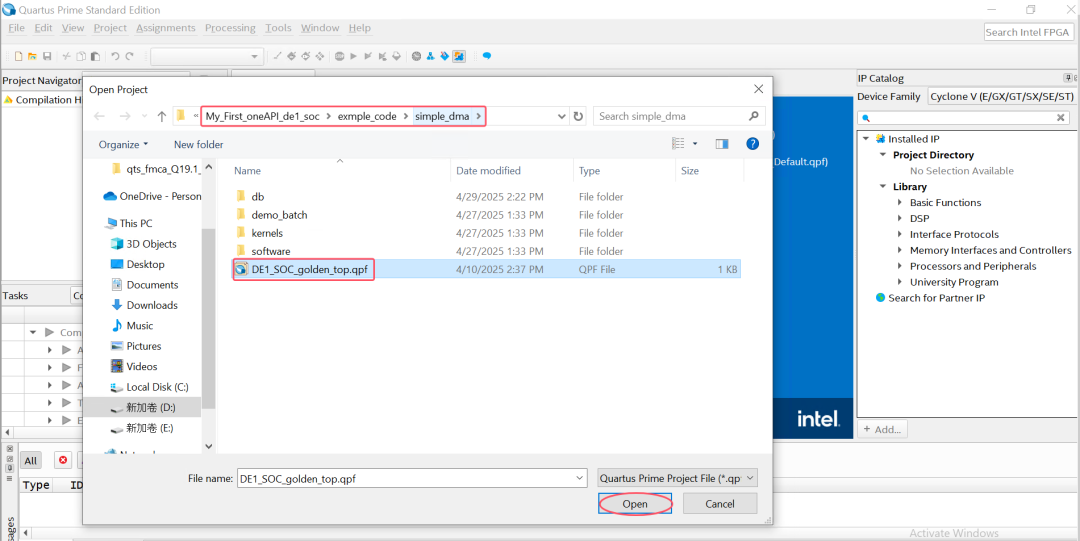

3. 打开My_First_oneAPI_de1_socexmple_codesimple_dma路径下的Quartus工程。

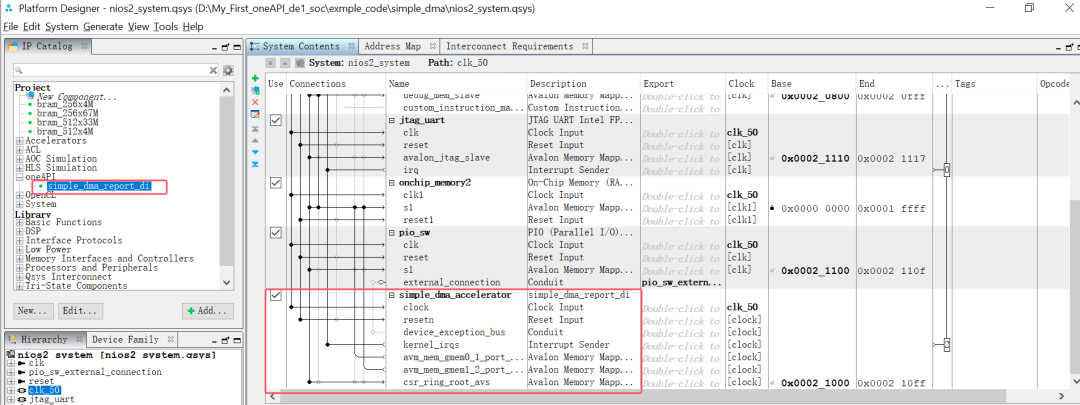

4. 从Quartus Tools菜单栏里打开Platform Designer,并打开simple_dma/nios2_system.qsys工程。

5. 在nios2_system.qsys里添加oneAPI -->simple_dma_report_di IP,并按下图所示连接,再完成Assign Base Addresses。

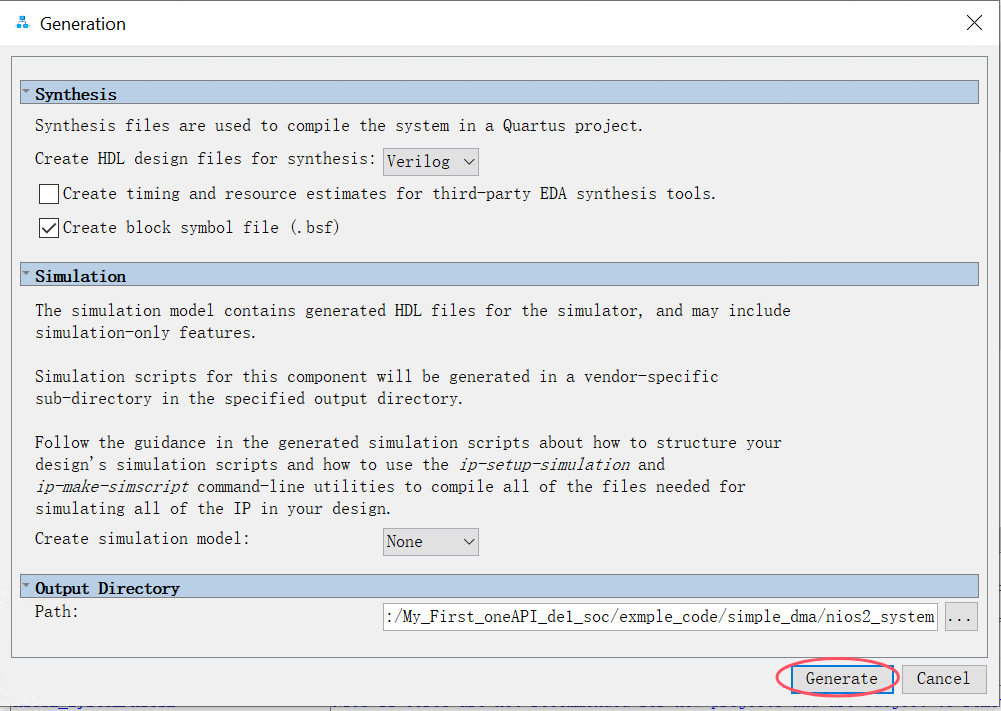

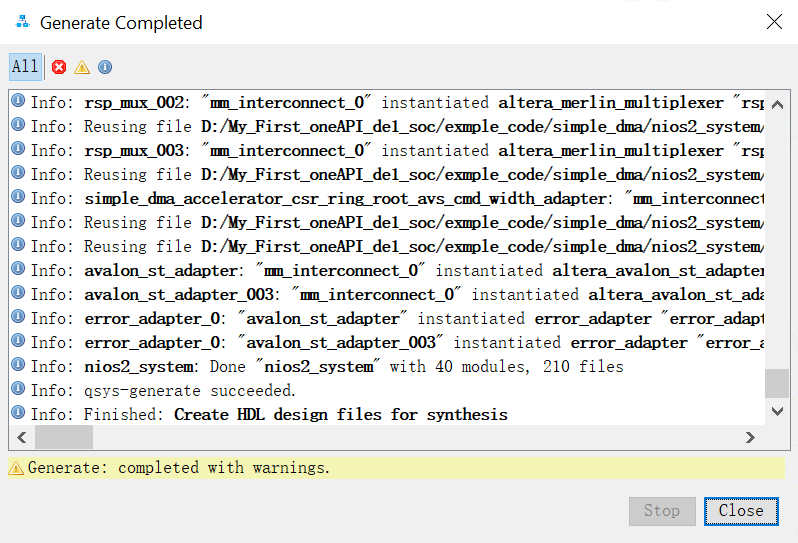

6. 点击Generate HDL-->Generate,生成HDL代码。

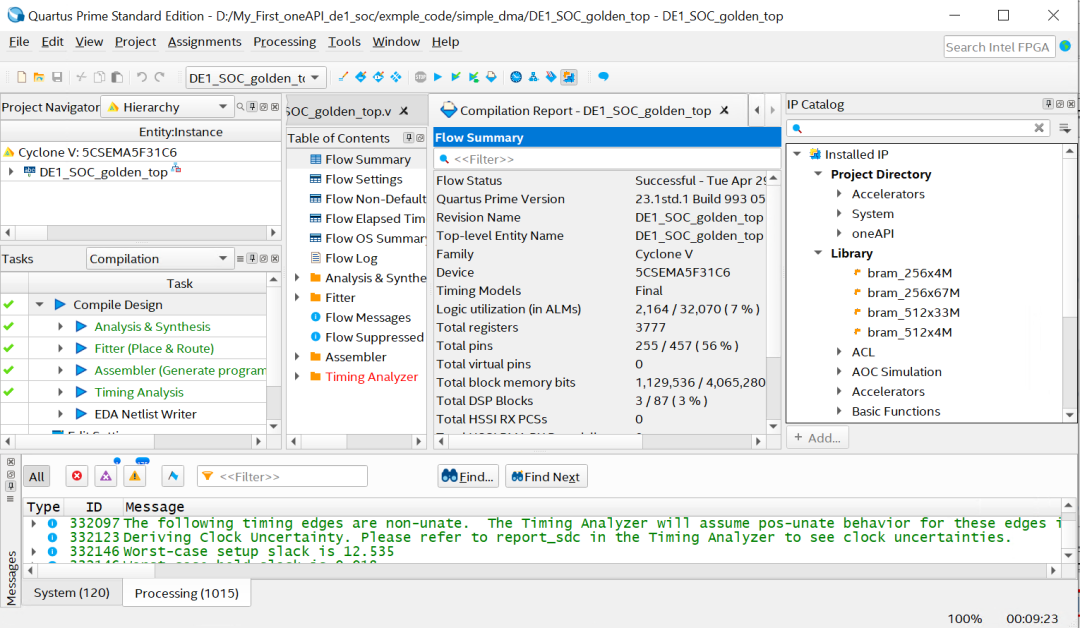

7. 编译Quartus工程。

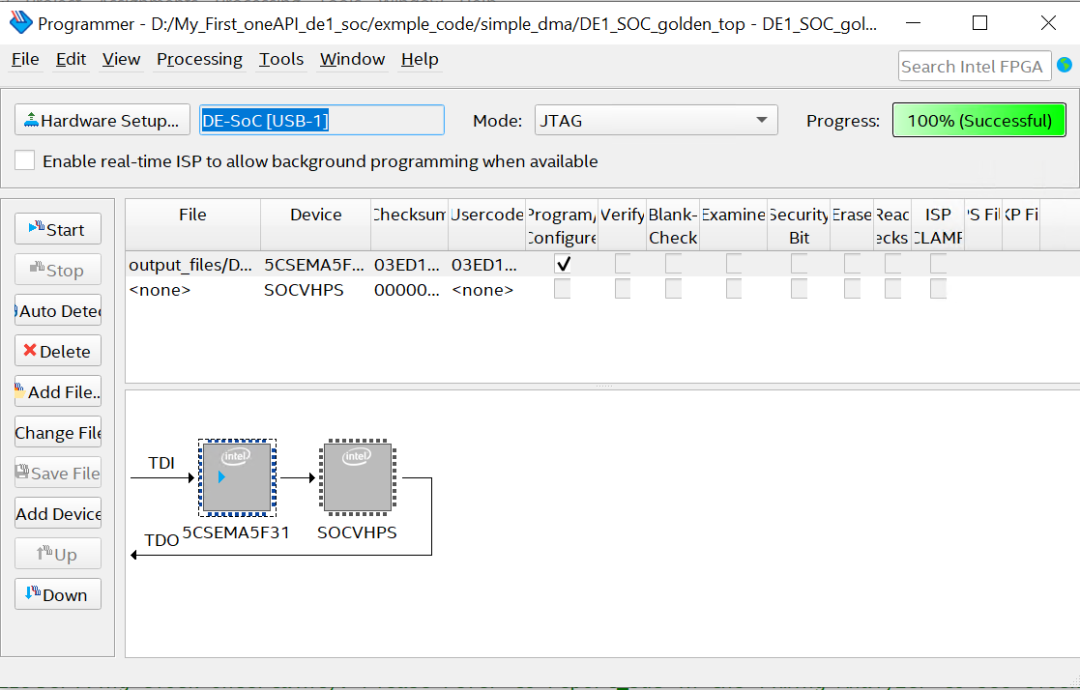

8. 将编译生成的.sof文件烧录到FPGA。

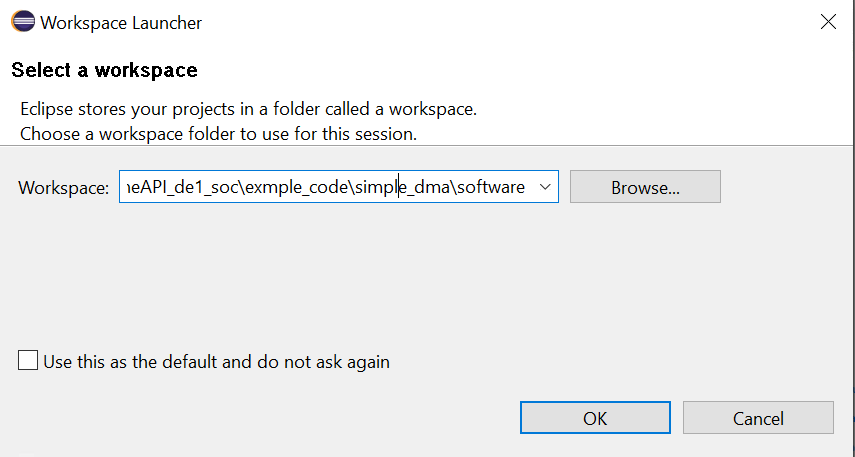

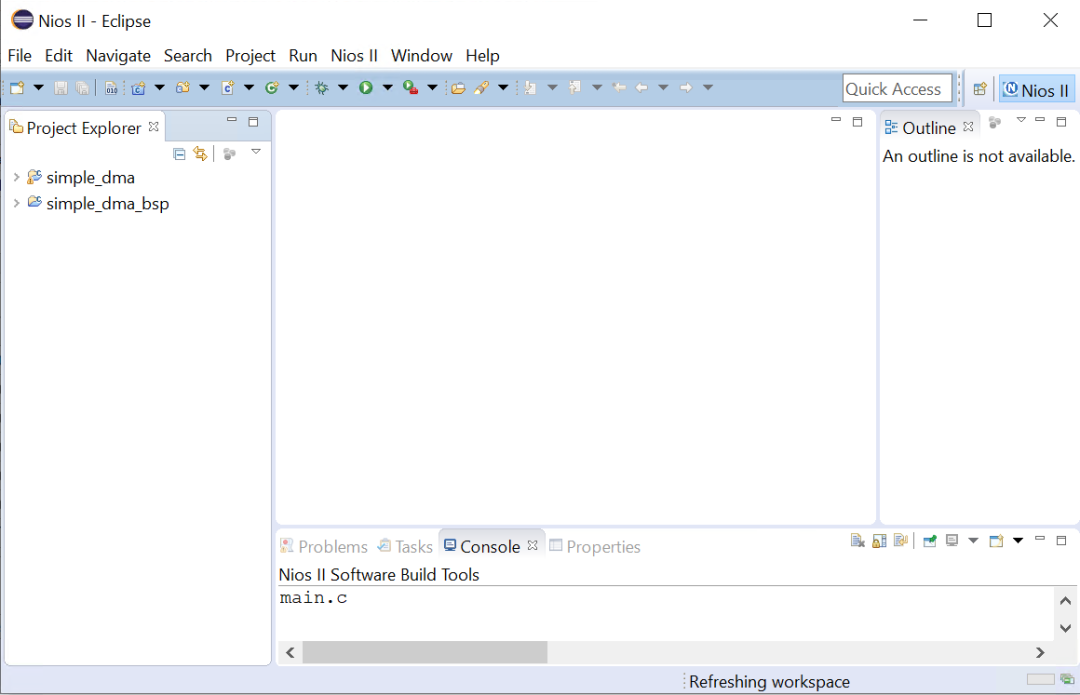

9. 从Quartus Tools里打开Nios II Software Build Tools for Eclipse,workspace切换到simple_dma/software。

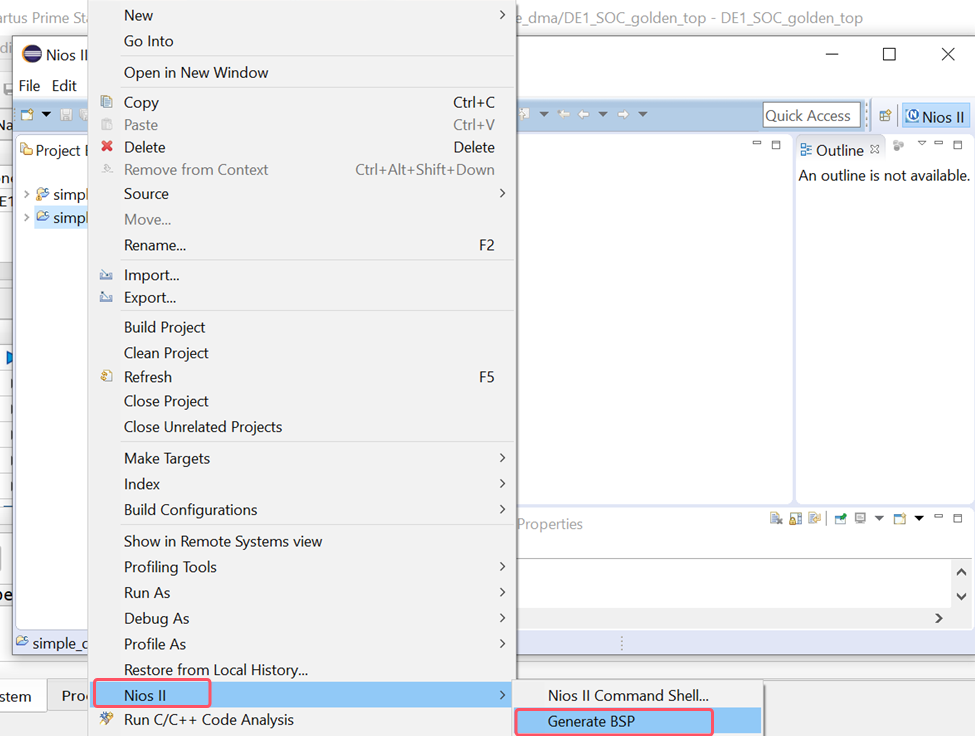

10. 右键点击simple_dma_bsp,选择Nios II > Generate BSP。

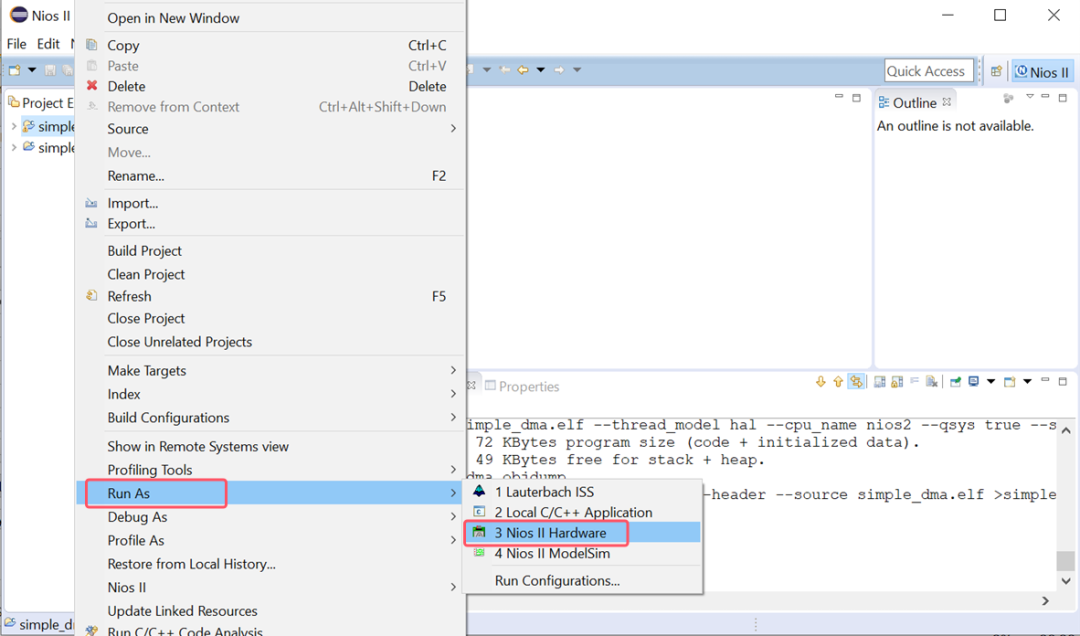

11. 右键点击simple_dma -->Run As --> 3 Nios II Hardware。

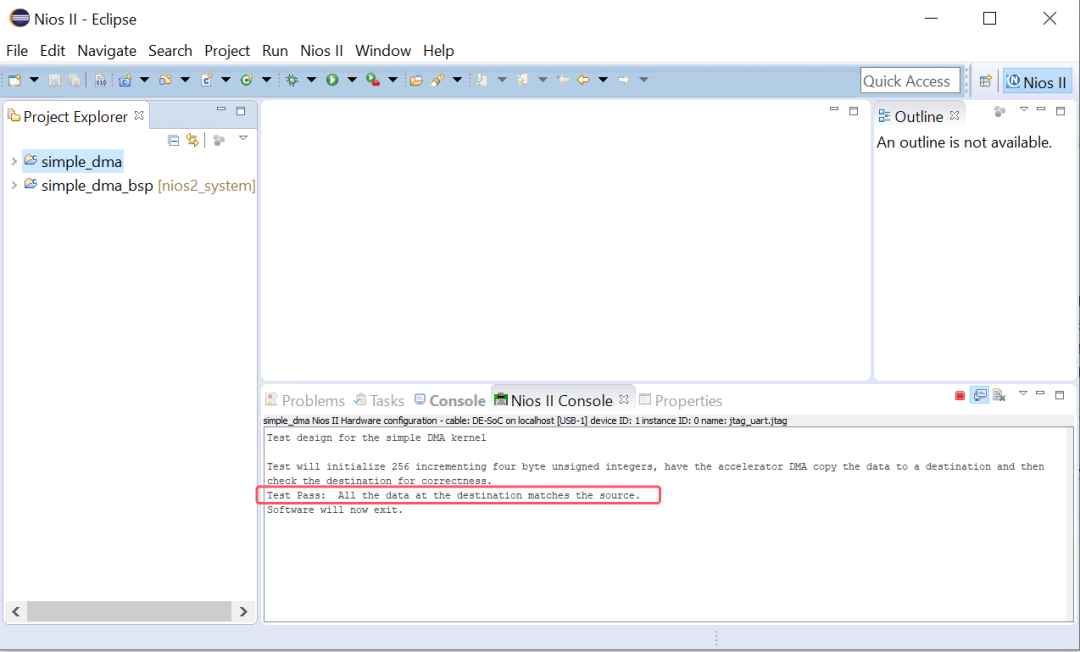

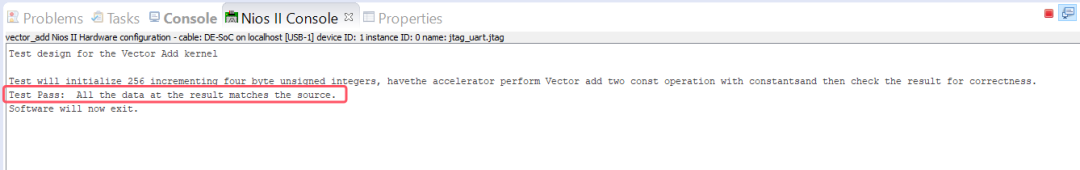

12. 在Nios II Console终端上会显示程序运行结果。

二、修改Simple DMA为Simple Adder

本节通过对Simple DMA设计进行扩展,添加基本算术功能,将其转换为Simple Adder。在保留原有DMA数据传输机制的同时引入两种类型的常量输入: c1--通过conduit接口提供;c2--通过CSR(Control and Status Register)配置。

在传输过程中,这些常量会被添加到数据中,这为如何在FPGA上集成数据处理和控制逻辑提供了一个示例。

接下来我们将解释如何配置和使用conduit接口与CSR接口以及它们之间的差异,并演示如何在Platform Designer中连接这些接口。我们还将介绍完整的开发流程,包括从SYCL(基于 C++ 的开放标准,用于简化异构计算如 CPU、GPU、FPGA 等并行设备的编程)示例代码编译到IP生成、Quartus集成、硬件配置以及在FPGA上验证结果。

conduit接口

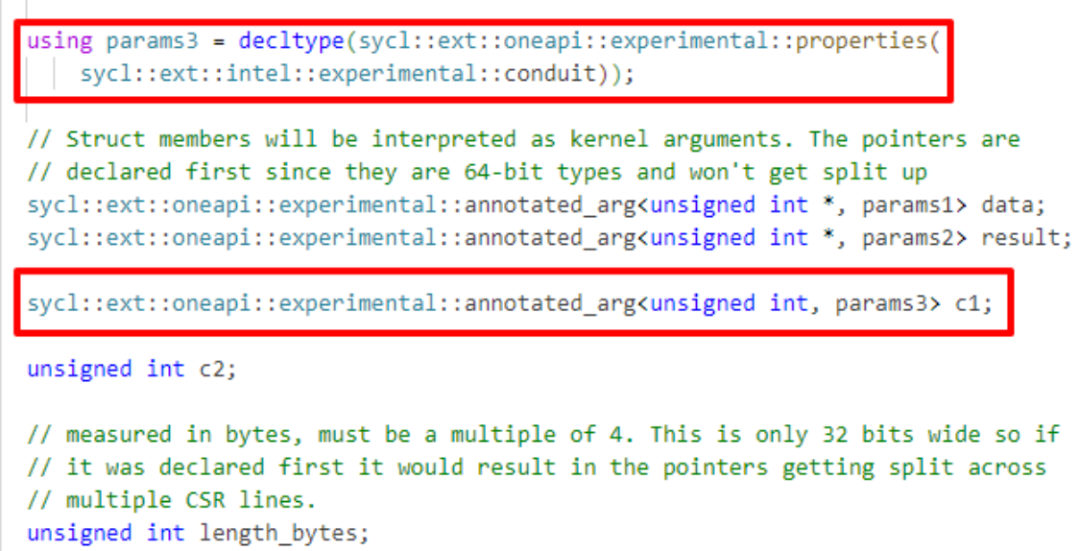

SYCL示例代码(My_First_oneAPI_de1_socexmple_codevector_addkernelsvector_addsrcvector_add.cpp)如下,将其配置成conduit。

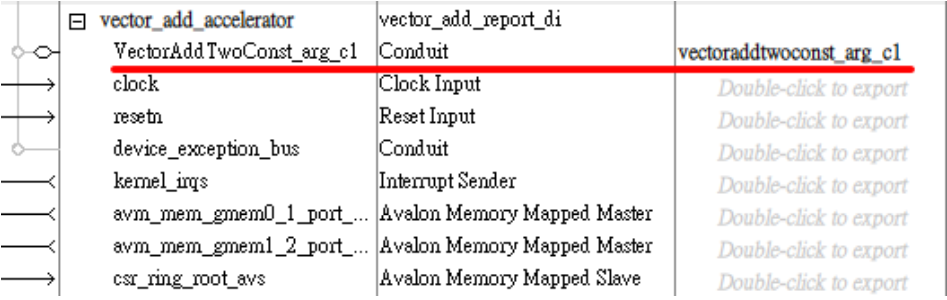

将代码转换为RTL IP后,该接口就可以在Platform Designer中看到。

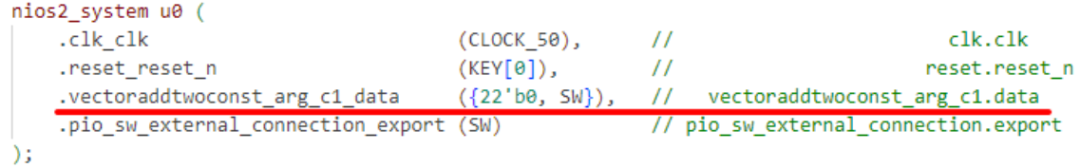

导出conduit接口,并在DE1_SOC_golden_top.v文件中例化连接到DE1-SoC开发板的滑动开关。

控制状态寄存器

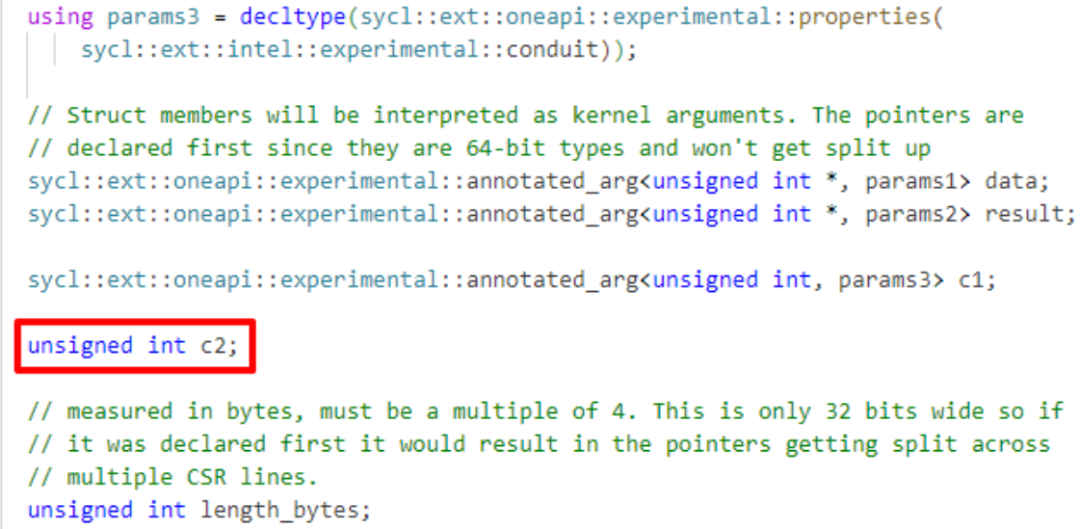

常量c2使用控制状态寄存器(CSR)来定义。在内核中声明此变量时,不需要额外的参数,默认为控制状态寄存器(CSR)。

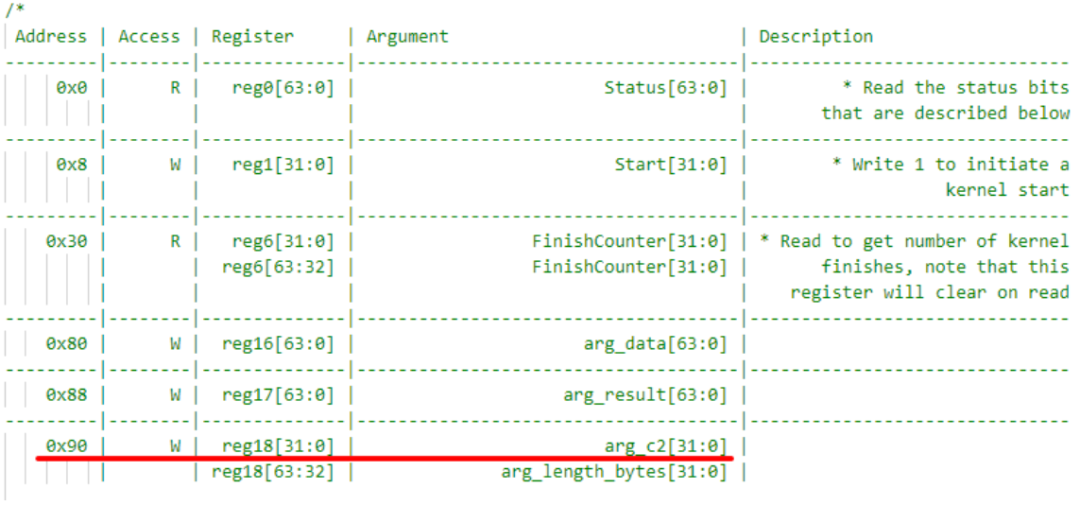

c2的寄存器偏移自动产生,可在kernels/vector_add/build/vector_add.report.prj/include/kernel_headers/VectorAddTwoConst_register_map.h中找到。

测试步骤

按照以下步骤在DE1-SoC开发板的FPGA上实现并部署Simple Adder。

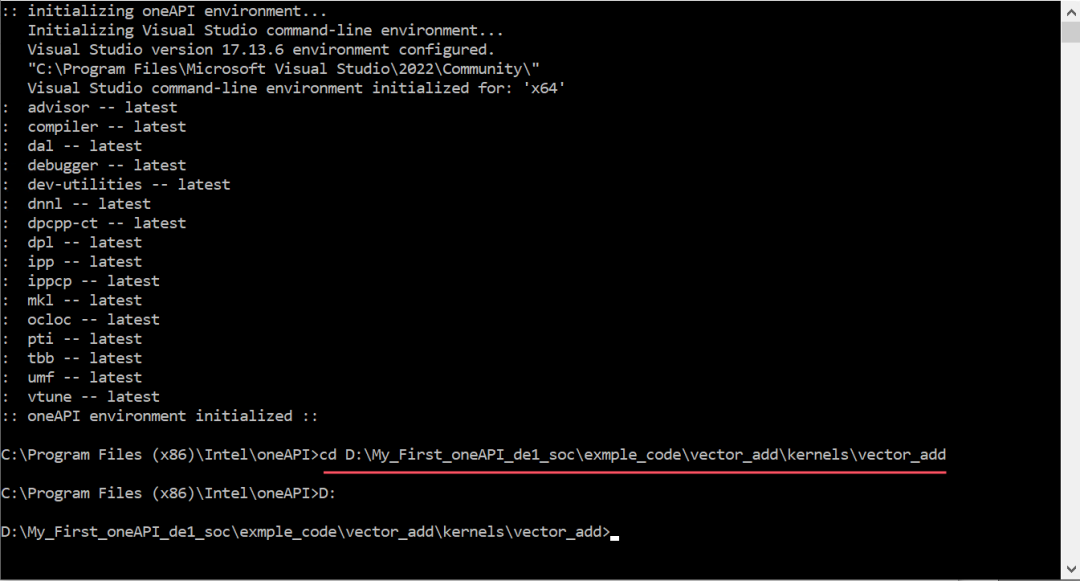

1. 打开Intel oneAPI 命令窗口,执行chcp 65001命令将语言编码更改为UTF-8,并切换到My_First_oneAPI_de1_socexmple_codevector_addkernelsvector_add路径。

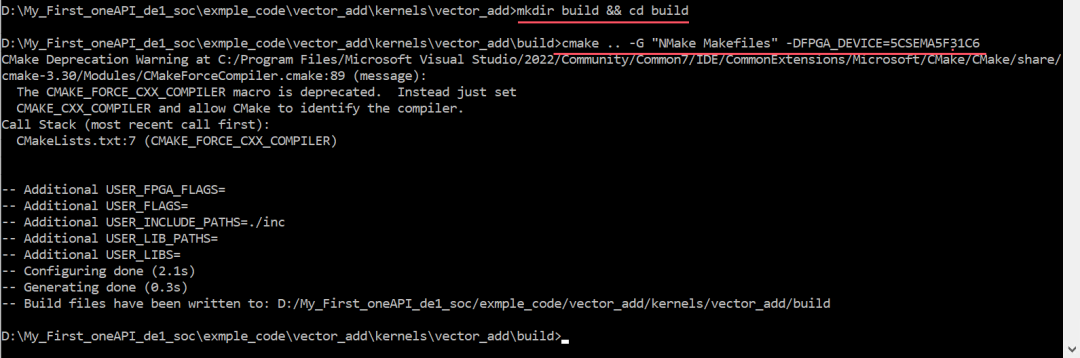

2. 执行以下命令创建并切换到build文件夹,以及指定FPGA为DE1-SoC开发板的5CSEMA5F31C6。

mkdir build && cd build

cmake .. -G "NMake Makefiles" -DFPGA_DEVICE=5CSEMA5F31C6

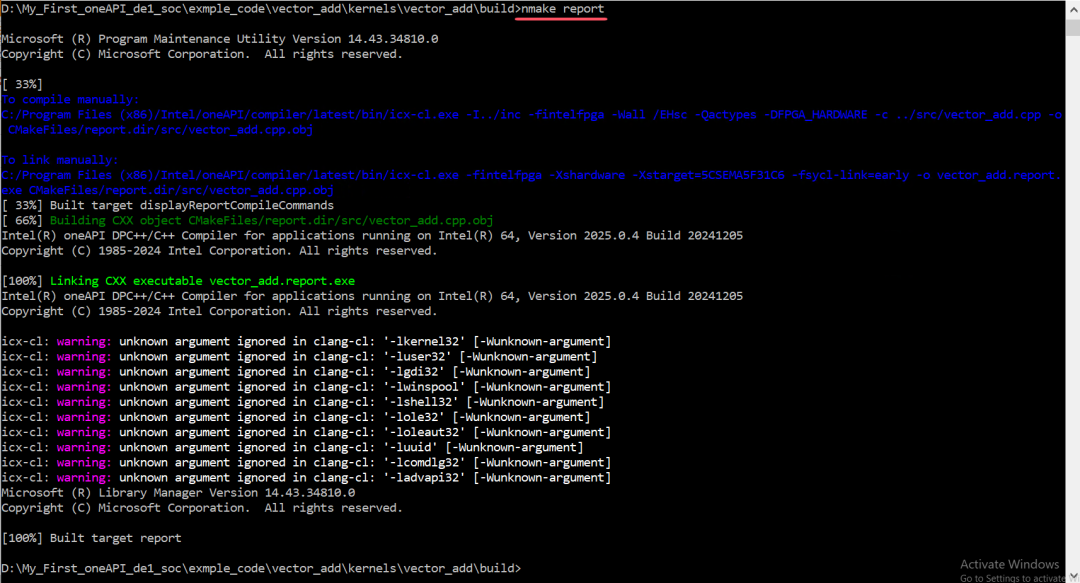

3. 执行nmake report命令编译Simple Adder IP,生成IP组件以及优化报告。

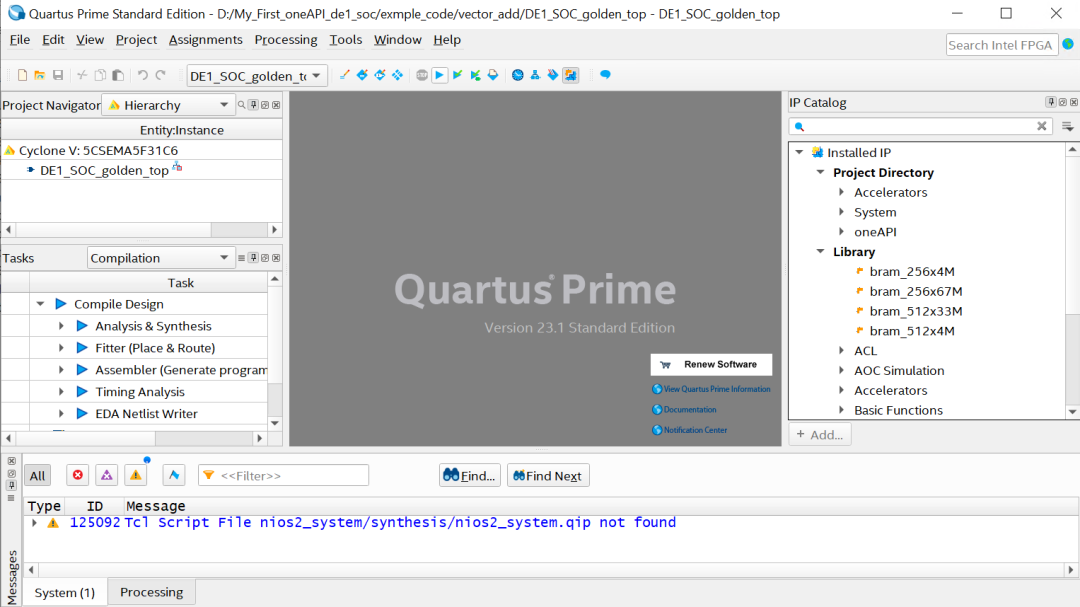

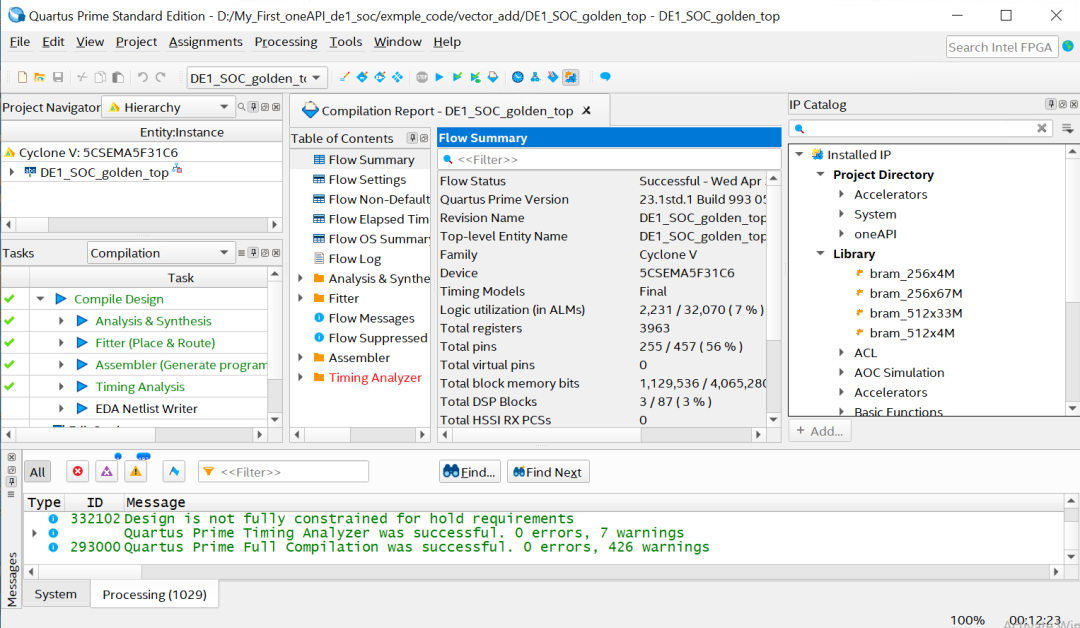

4. 打开DE1_SOC_golden_top.qpf工程。

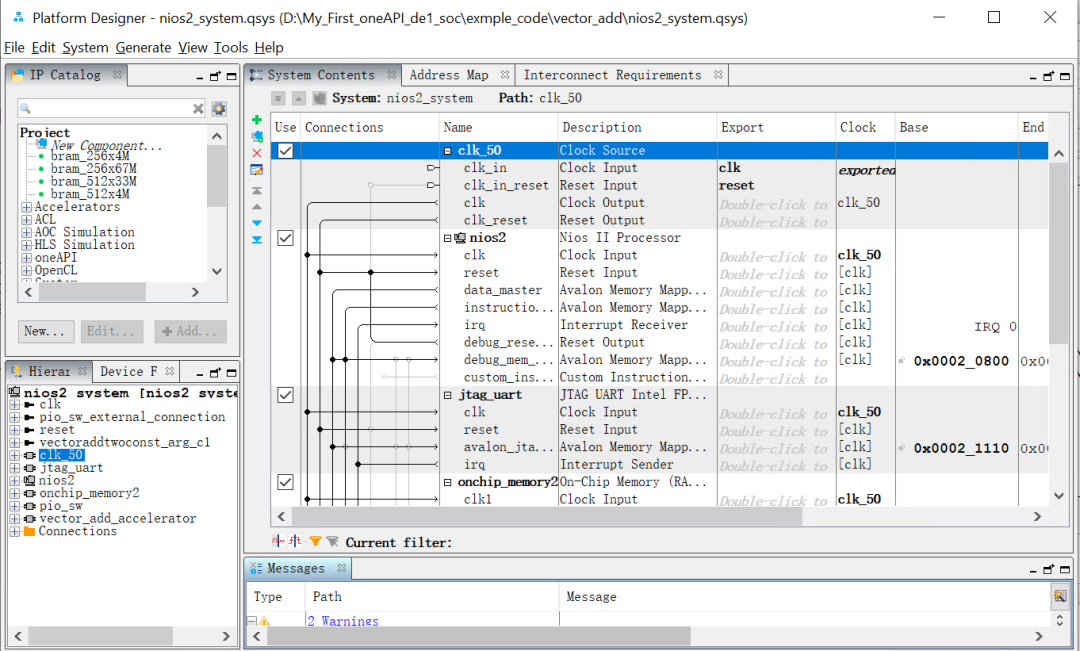

5. 打开vector_add/nios2_system.qsys工程。

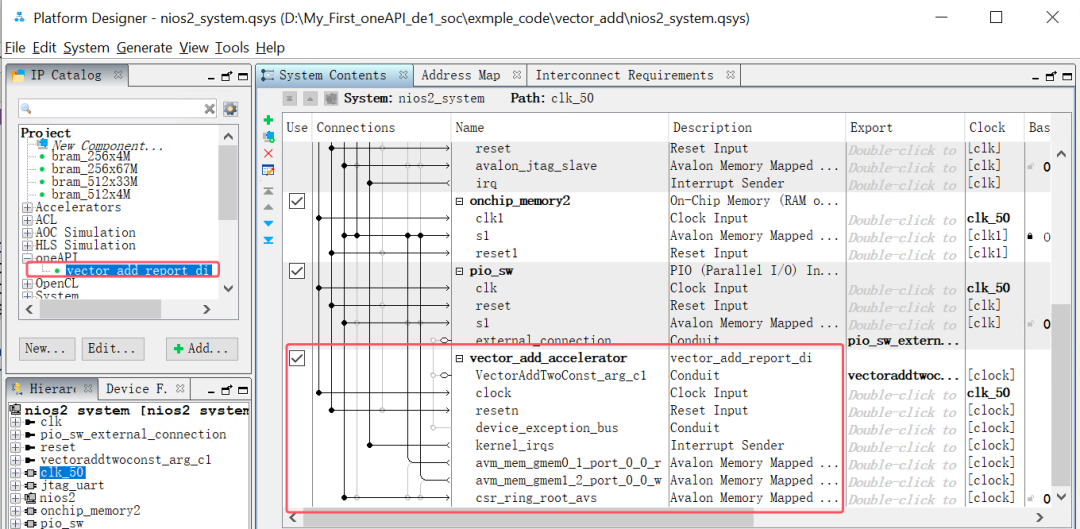

6. 添加oneAPI里的vector_add_report_di,并按下图所示连接。

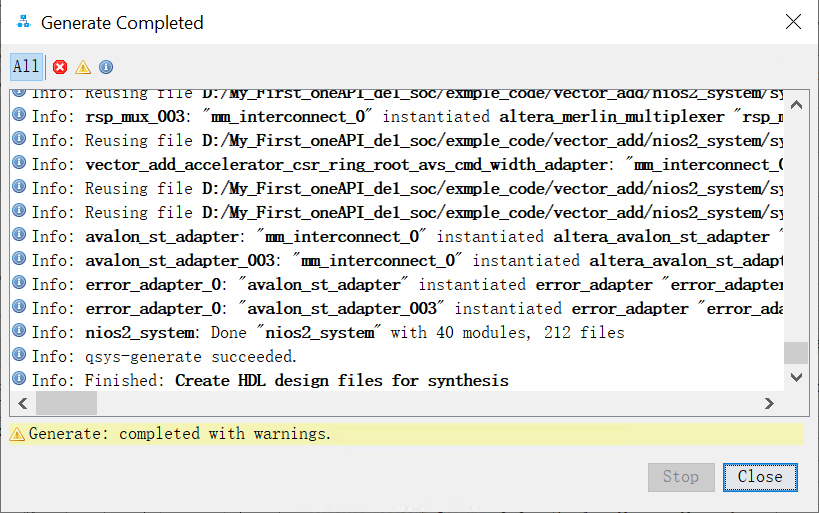

7. 点击Generate HDL-->Generate生成HDL。

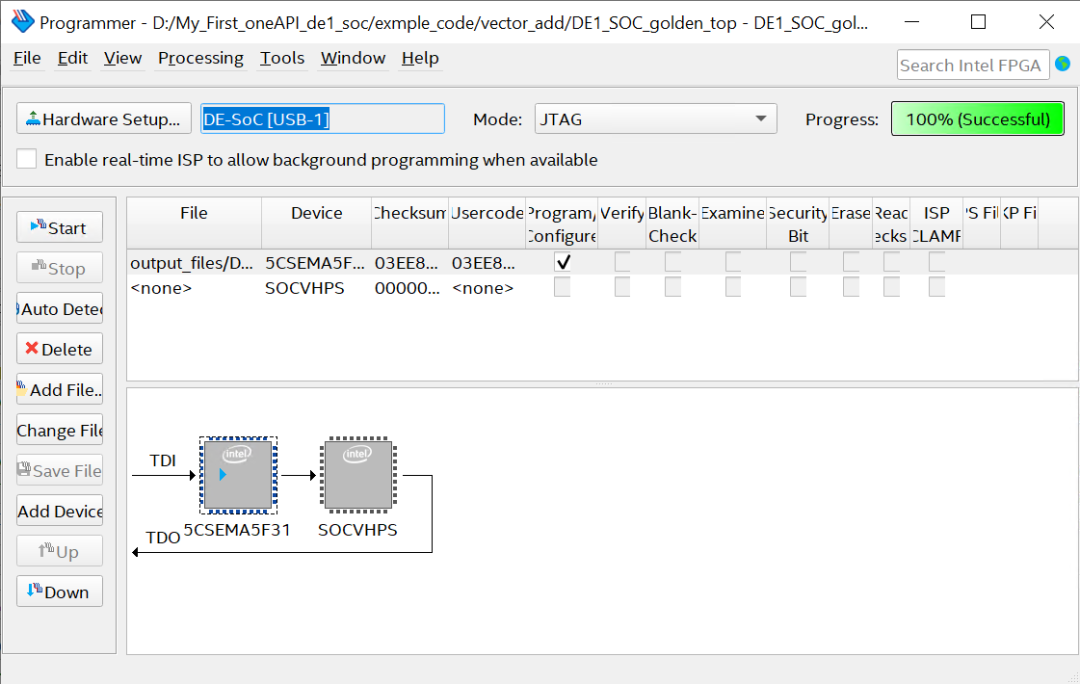

8. 编译Quartus工程,并将生成的.sof烧录到FPGA。

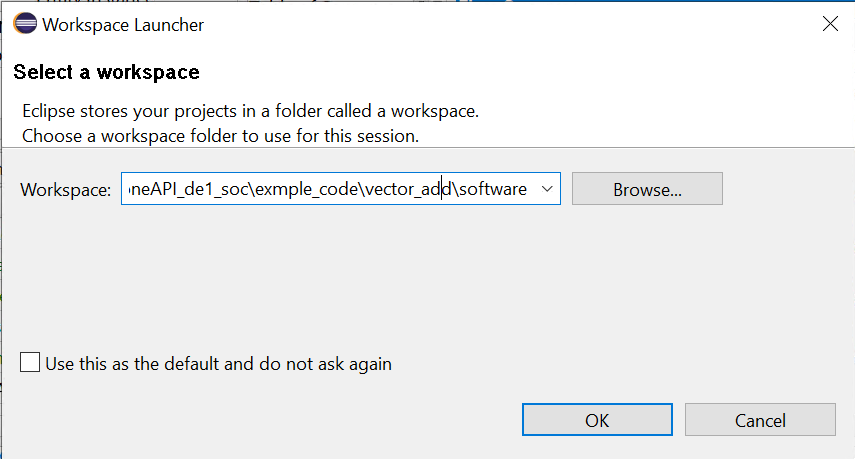

9. 运行Nios II Software Build Tools for Eclipse,将workspace切换到vector_add/software。

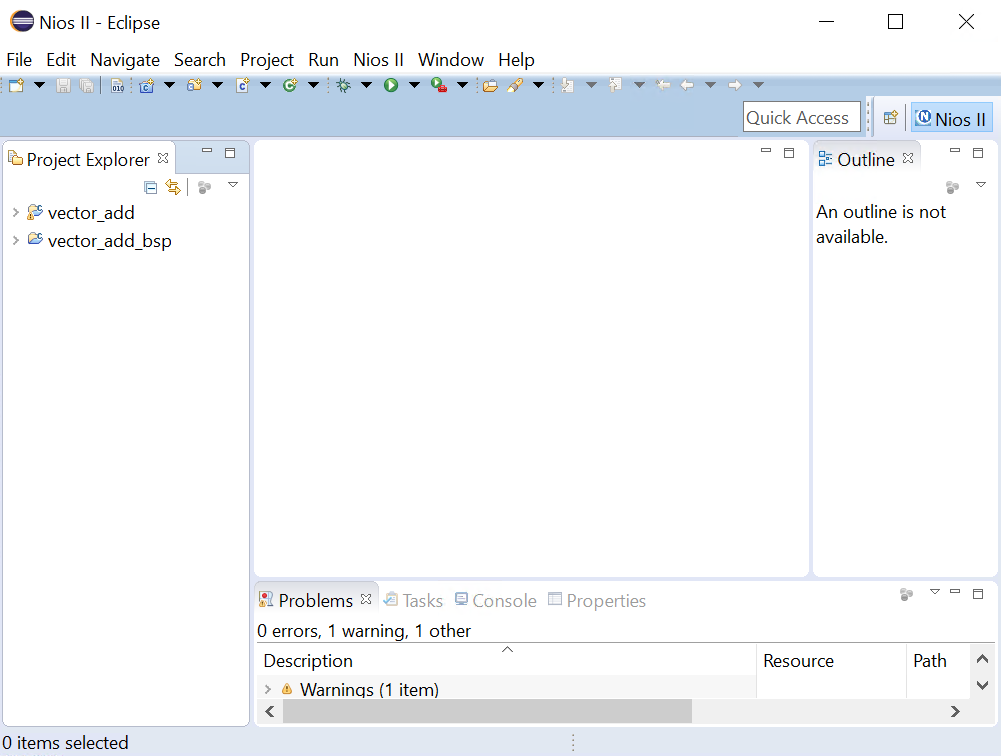

10. 右键点击vector_add_bsp,选择Nios II -->Generate BSP,生成BSP;右键点击vector_add选择Build Project编译工程。

11. 右键点击vector_add,选择Run As > 3 Nios II Hardware,烧录.elf文件运行工程。然后在Nios II Console终端显示结果。

三、Q&A

1. Quartus Standard v23.1的Nios II Software Build Tools for Eclipse如果无法运行起来,请参考Getting Start Install Eclipse IDE into Nios EDS文档里的步骤安装Eclipse IDE。

2. vector_add Nios II工程无法编译,请参考Getting Start Install WSL安装WSL。

![[快讯]华信永道:东北证券股份有限公司华信永道(北京)科技股份有限公司募投项目延期的核查意见](https://ashou.cn/zb_users/theme/Jz52_mrcms/style/images/noimg.png)